引言

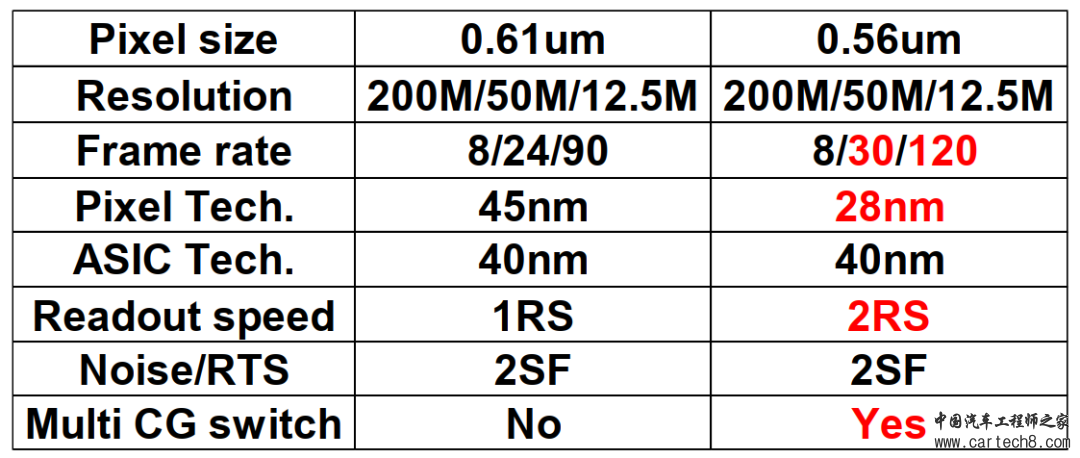

在之前的文章中《CIS|豪威200MP移动设备图像传感器技术论文解析》,我们介绍了豪威科技在移动端200Mega Pixels产品的技术论文,讲解了消费级CIS传感器的基本架构、工艺以及与车载应用不同之处,今天我们将继续借其下一代pixel size为0.56μm的技术论文,讲解其技术演变。在本文中,我们描述了一种在28nm工艺中实现的具有0.56?m像素的200M像素CMOS图像传感器。该像素技术是继我们的0.61?m像素之后的下一代发展。该传感器表现出5.5ke的全阱容量,暗电流和读取噪声比我们的上一代像素更低。此外,与我们的上一代像素相比,该传感器表现出类似的量子效率(QE)和相位检测自动聚焦(PDAF)性能。该传感器还实现多种功能,包括切换转换增益和高速读出。

1. Introduction

在CMOS图像传感器(CIS)领域,像素小型化推动了产品创新。在保持性能的同时,追求不断缩小像素大小,这是近年来CIS发展的基础。对高分辨率移动图像传感器的需求不断升级,移动CIS产品的分辨率在不到5年的时间内从24Mp提高到200Mp。尽管实现了低于可见光波长的像素间距缩放,但由于图像信号处理的逐步改进,始终实现了更好的图像质量。虽然像素缩小以较小的形状因子提供更高的像素数,但像素小型化和整体性能之间存在权衡,因为光接收面积的减少会导致CIS性能下降。高分辨率图像传感器几乎完全使用晶片堆叠来实现,其中像素和读出电路被分离到独立的晶片上。此外,高分辨率像素读出需要更多的选择线进行控制,这增加了电容,导致读出速率较低。双列选择能够在不增加位线数量的情况下实现快速像素binning,实现快速读出而无需额外电路。小像素图像传感器经常受到较低的全阱容量(FWC)的影响。因此,需要强大的隔离电位屏障来缓解这一问题。在本文中,我们提出了一种0.56?m像素、200MP堆叠CMOS图像传感器,该传感器使用新的CIS专用28nm工艺开发。缩小工艺节点释放了芯片空间,为其他设备和功能提供了空间,如可切换转换增益(SCG)和用于低噪声和高速读出的电路。这项工作中开发的0.56um像素在不牺牲暗性能的情况下实现了高FWC。与0.61?m的前代相比,在没有图像滞后或晕染的情况下获得了更高的FWC,而暗电流和白色像素(WP)保持可比性。该设备能够采用具有可切换转换增益的像素binning模式,提供高动态范围和FWC以产生更高的图像质量。共享浮动扩散(FD)用于16C binning模式以降低读取噪声。

2. 像素架构与技术

A. Pixel堆叠式工艺

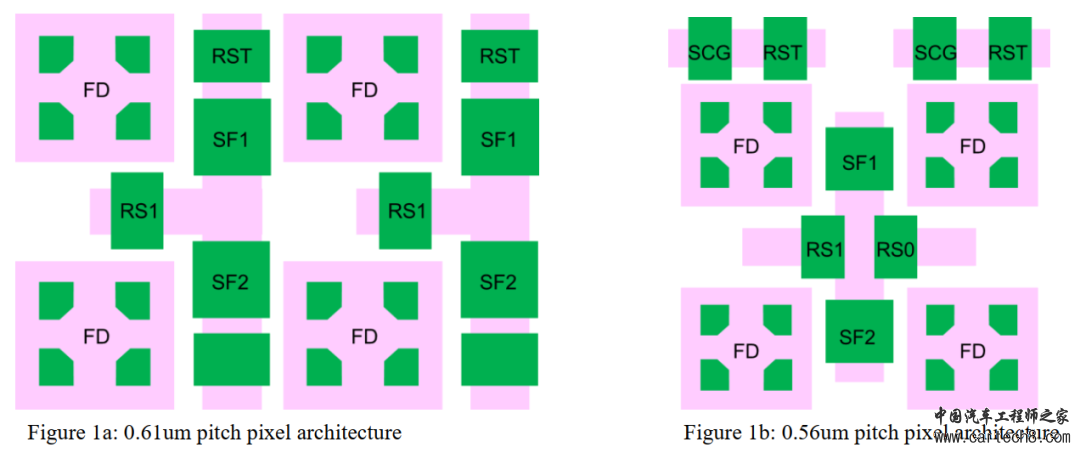

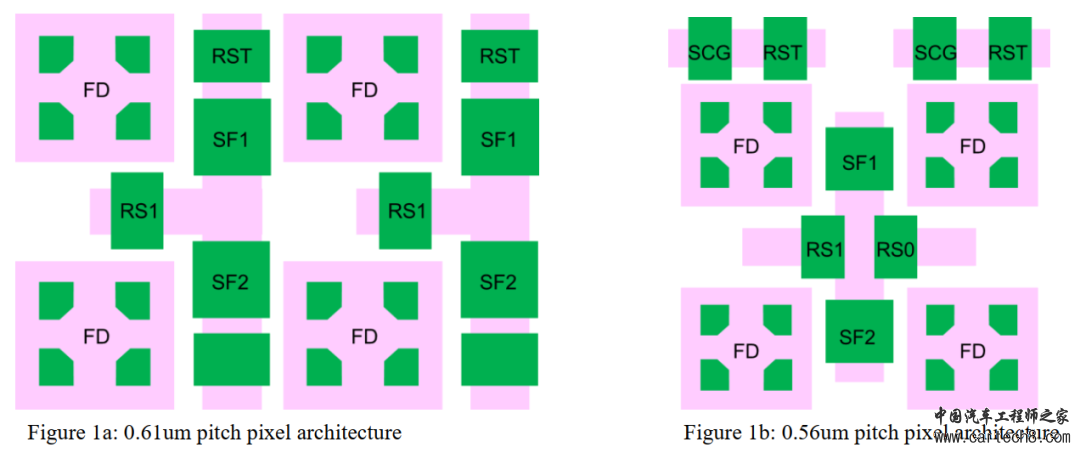

本文讨论的0.56?m像素开发采用了一种新的、独联体专用的28nm像素工艺节点,而不是上一代设备中使用的45nm工艺节点。逻辑芯片遵循我们以前的小像素堆栈传感器中使用的40nm处理节点。与0.61?m像素设计相比,0.56?m-Pitch设备受益于由CIS专用28nm处理节点启用的增强设计灵活性。由于28nm节点保留了芯片空间,该设备实现了额外的行选择晶体管,以实现快速读取。额外的布局策略用于改善噪音性能和更高的FWC。下图显示了这项工作中使用的0.61?m(Figure 1a)和0.56?m(Figure 1b)之间的像素晶体管布局比较。

Pixel对比每个晶体管分别由浅沟隔离(STI)隔离,而每个像素分别由改进的背深沟隔离(BDTI)、最大限度地减少泄漏和光学串扰隔离。通过采用CIS专用28nm处理节点,每组像素实现并联SFS以增加SF宽度,该SFS与2排精选晶体管设计一起工作,以最大限度地提高大型200MP设备的读取。如果没有这样的策略,这样一个大型设备可能会阅读缓慢;实现了垂直传输门(VTG)结构,将光电二极管更深地转移到硅区域,28nm像素处理为晶体管在0.56?m间距像素的有限空间中的设计和放置提供了更大的灵活性。这还允许在像素内放置额外的晶体管,以支持高动态应用的可切换转换增益。

B. Pixel架构

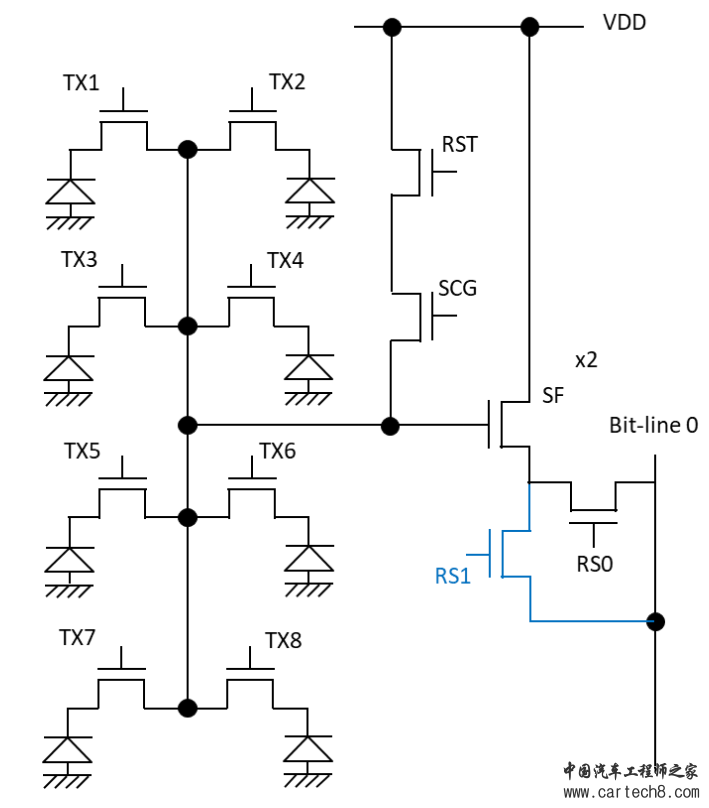

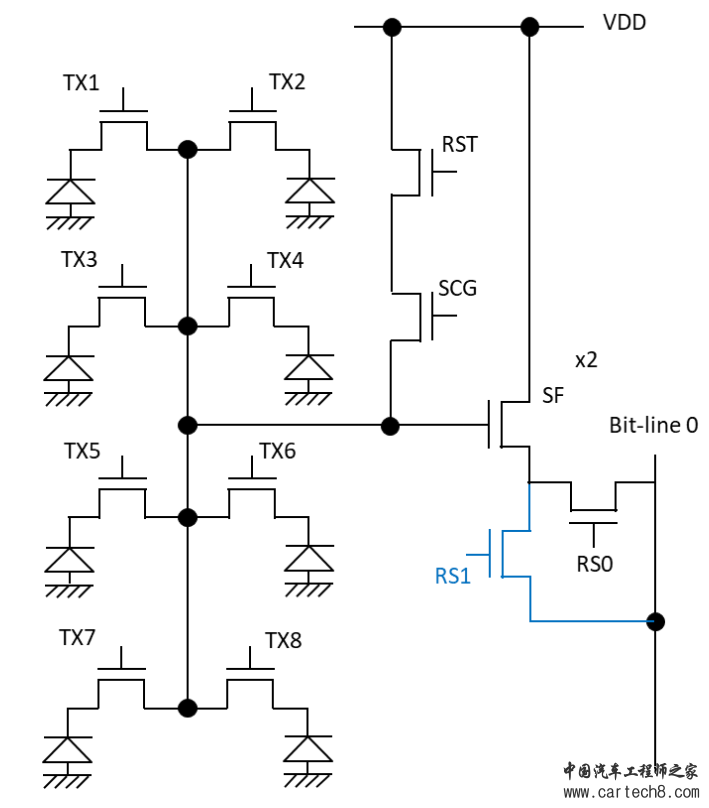

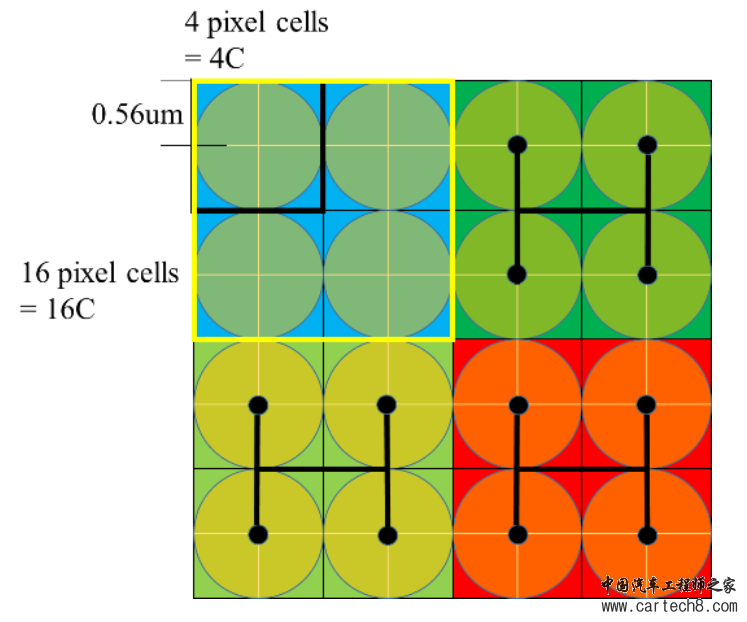

像素阵列大小为200兆像素(16384(H)x12288(V)),其光学格式为1/1.395,像素间距为0.56?m。采用2x4共享像素架构,如下图中的电路示意图所示。

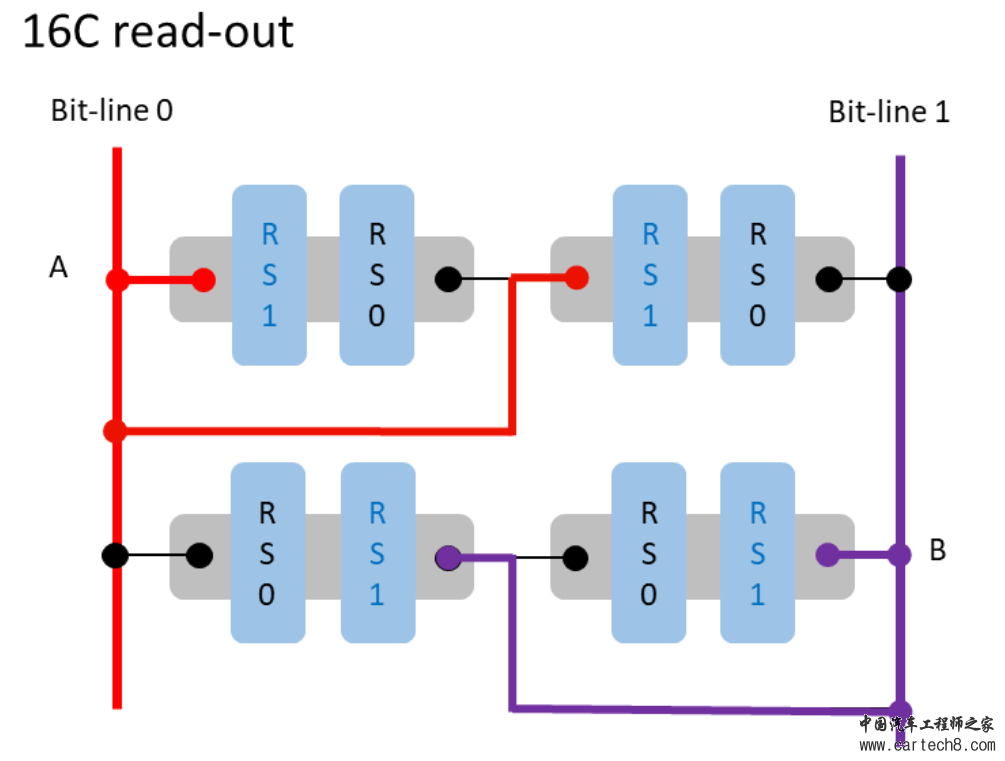

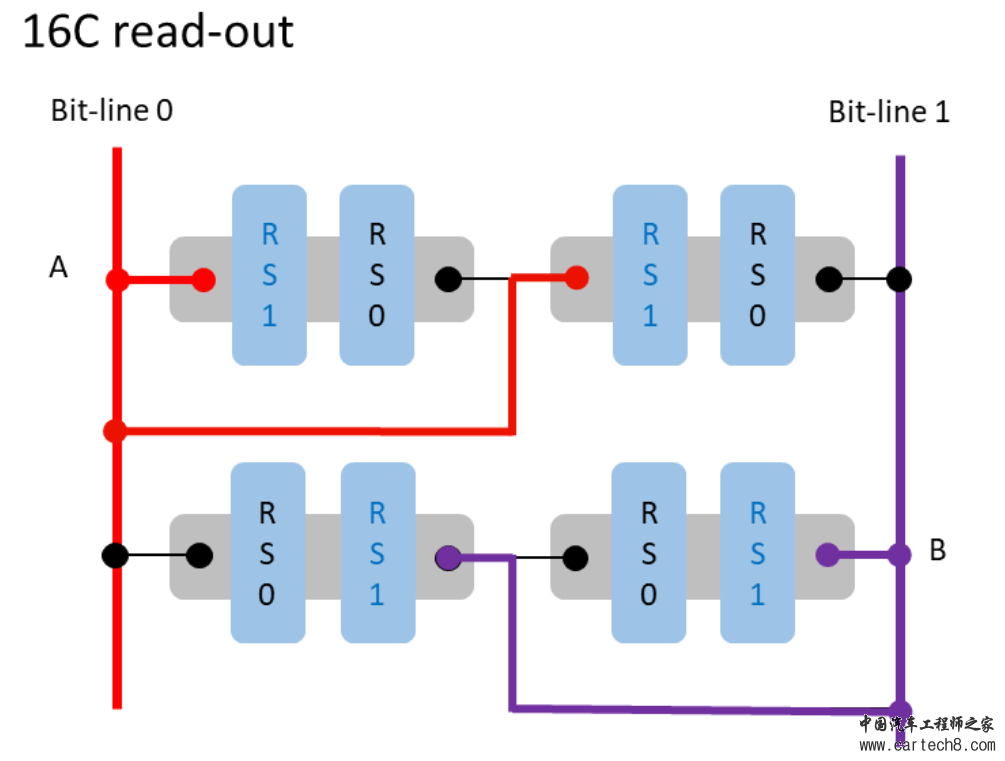

Pixel架构实现了一种新的2行选择晶体管设计,其中每个2x4共享像素由单独的控制信号RS0和RS1独立控制。在全尺寸或4单元模式中,RS0对左共享像素和右共享像素都是有效的,并且它们在FD处的信号通过两条独立的位线被单独地同时读出。在16C模式中,RS1对于左共享像素和右共享像素都是活动的,两个共享像素的RS1都连接到同一位线。交替行的RS1连接到单独的位线(下图中标记为“A”和“B”单元),保持两条位线的相同负载。

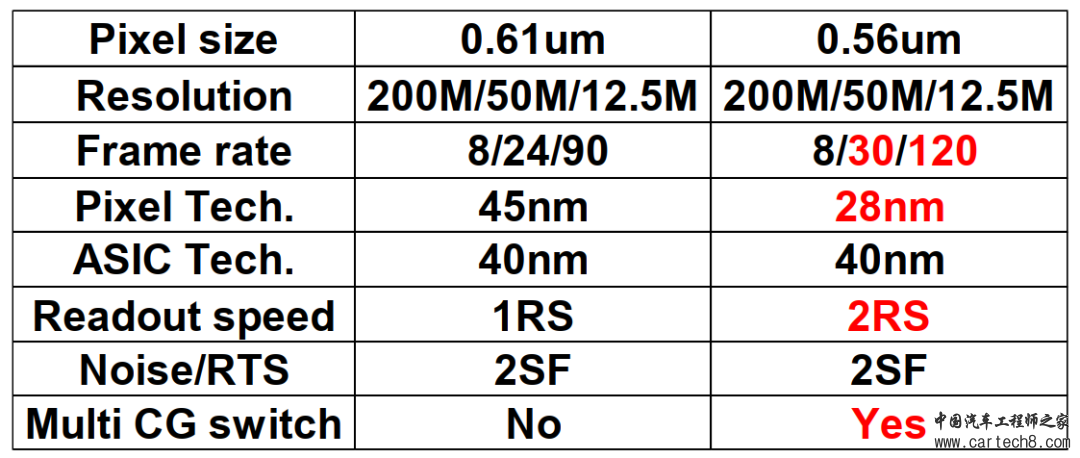

Readout这种交替的位线控制方案通过两条位线和两个列ADC读出两个16C binning的信号。这使得0.56?m器件的16C binning模式能够在不增加位线数量的情况下实现更快的读出速度。下表展示了0.61?m和0.56?m器件架构的比较:

性能对比

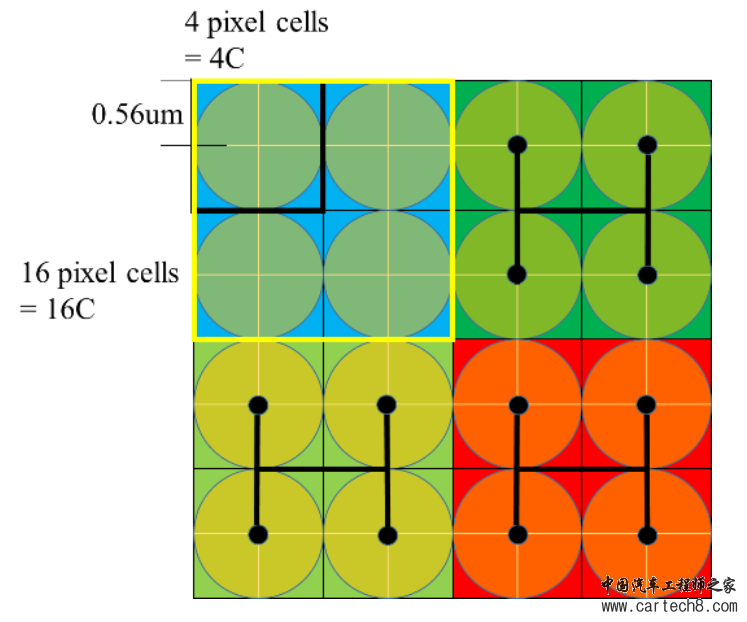

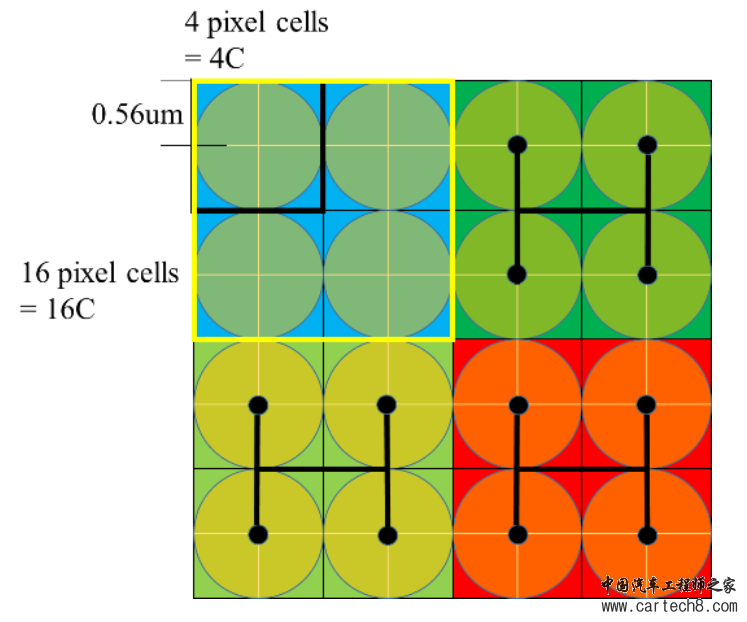

C. QPD和滤色器模式

由于较小的片上透镜(OCL)填充因子,小间距像素遭受显著的QE退化。QPD,或具有2x2 OCL的Quad Bayer编码,是一种在2x2像素阵列中使用一个OCL和相同滤色器的设计,可产生高分辨率和高动态范围的图像传感器。QPD是改进小像素图像传感器量化宽松的一项重要技术,并在本工作中实现,如下图所示:

QPD

3. 实验结果

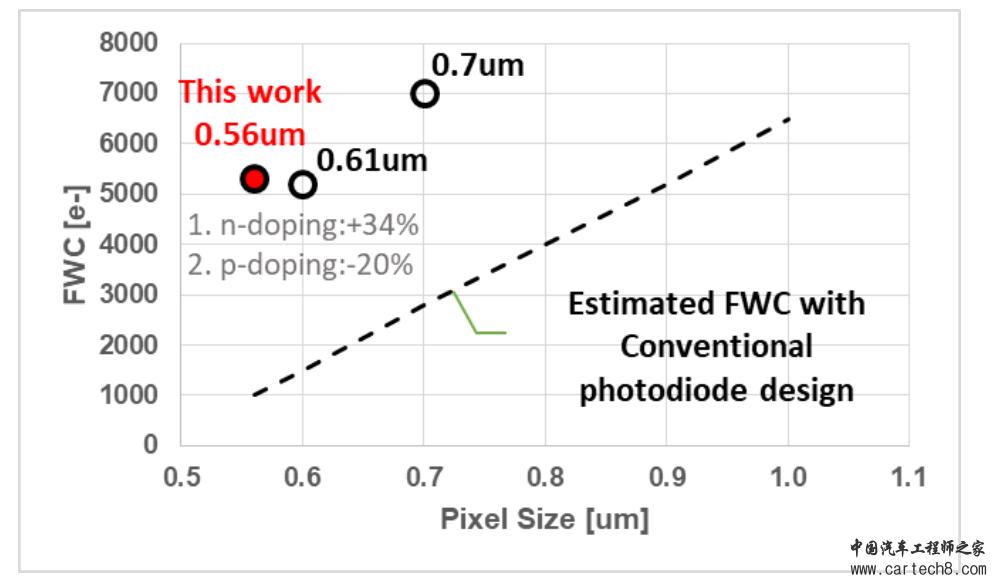

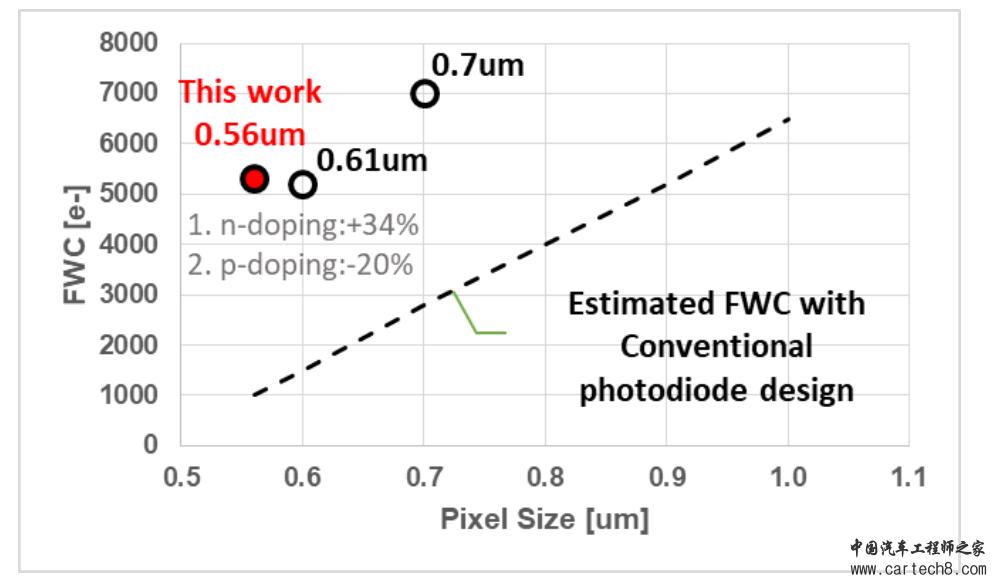

像素间距与FWC关系趋势图如下所示:

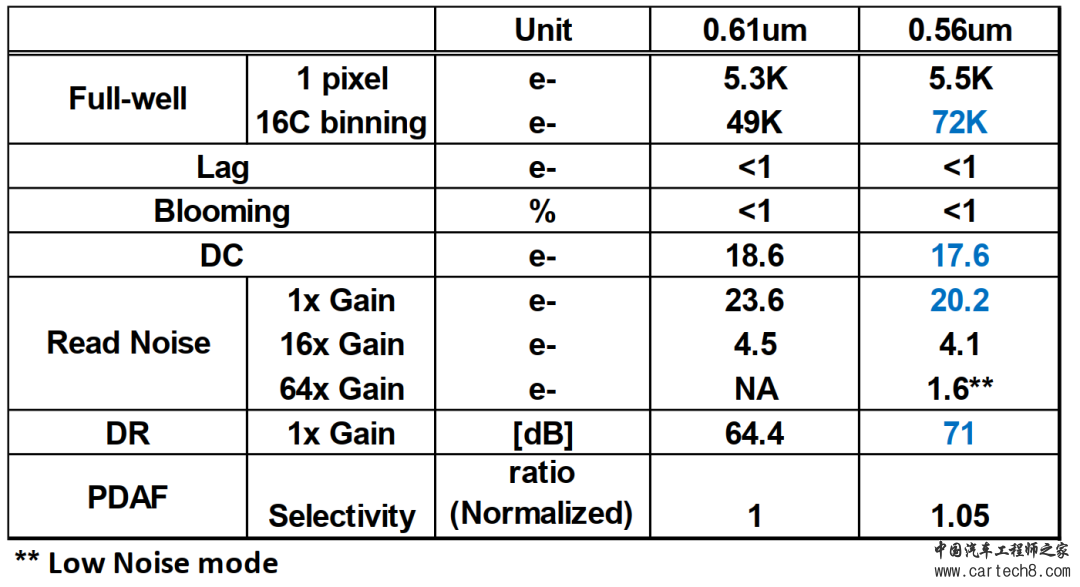

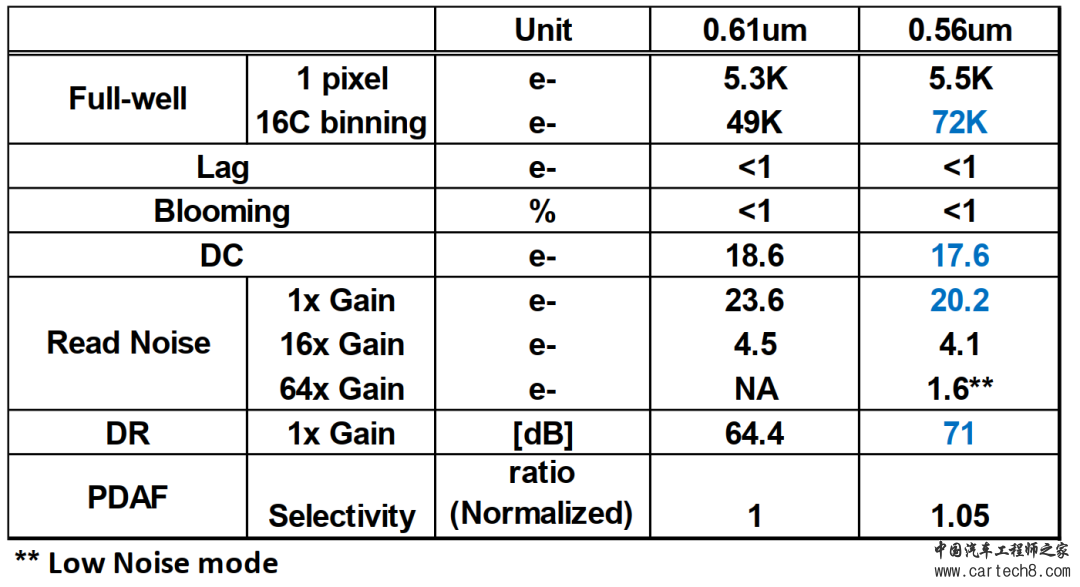

FWC趋势虚线表示通过基于1.0?m像素的简单像素面积缩放实现的FWC。空圆圈显示了我们上一代0.7?m和0.61?m技术的数据。0.7?m、0.61?m和0.56um器件显示的实际FWC远高于简单缩放预测的值。这种FWC增强是通过深光电二极管技术实现的,其中光电二极管电势位于更深的硅区域。通过采用该技术,0.56?m器件实现了5.5ke-FWC,没有滞后或开花。尽管我们增加了n型/p-型离子注入剂量,产生了更高的电场,但我们改进的BDTI技术减轻了表面缺陷的影响,实现了与上一代相当的暗电流和WP。其次,间距为0.61?m和0.56?m的器件之间的性能比较如下表:

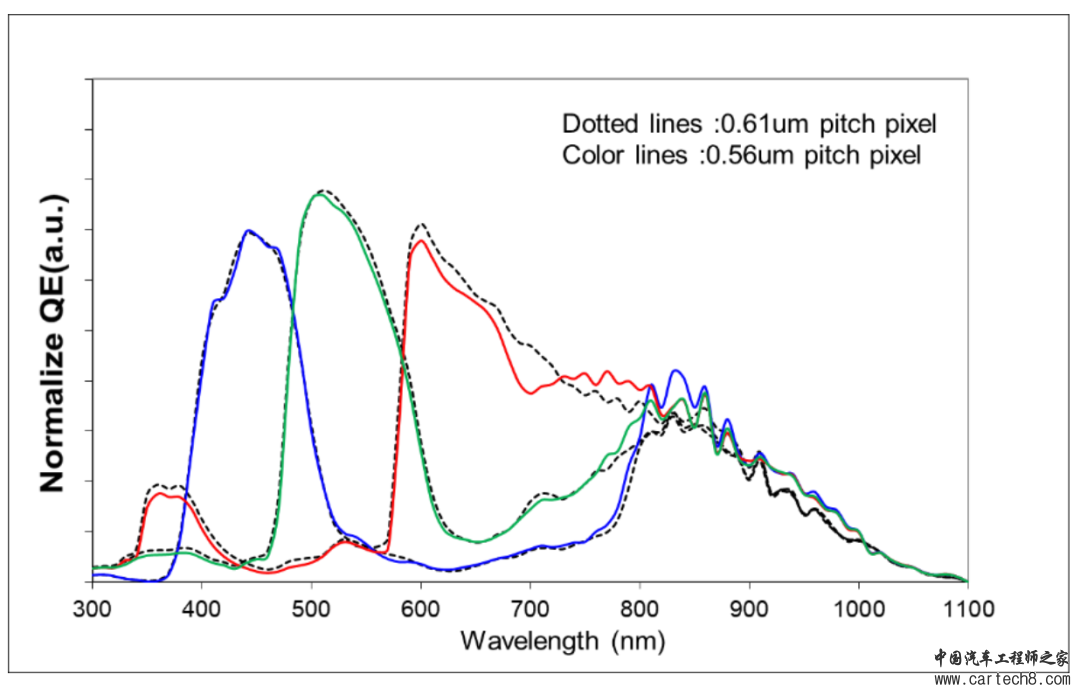

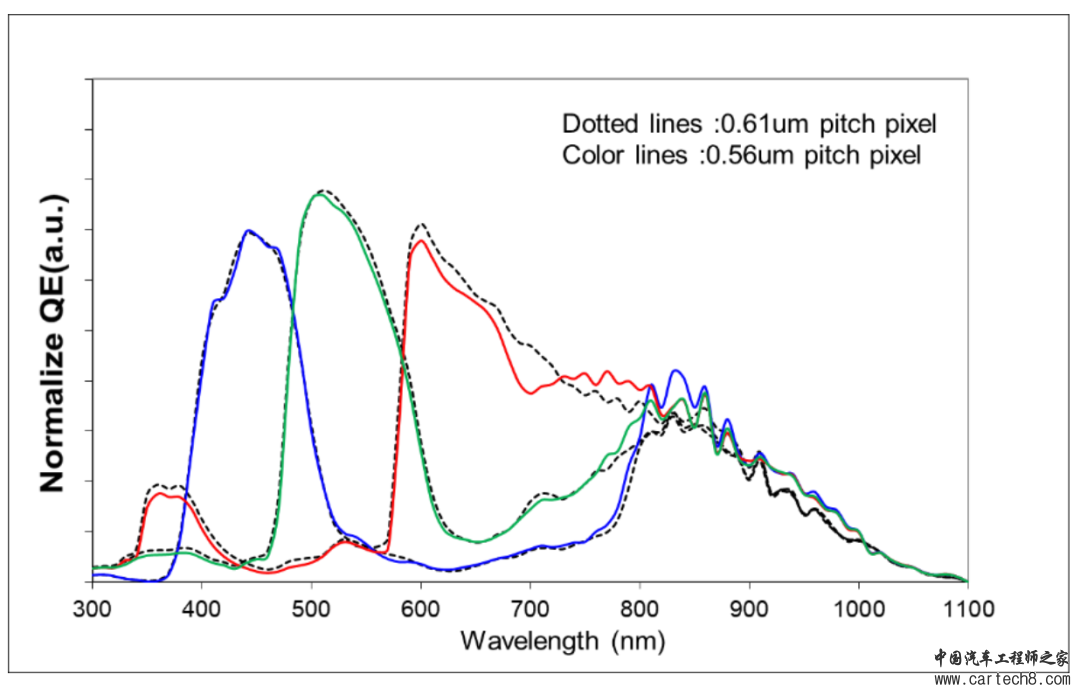

性能对比可以看出0.56微米间距的像素在所有方面都比0.61微米间距的器件表现出更好的性能,包括非常低的噪声水平和相位检测自动聚焦(PDAF)性能。另外,光学QE性能对比结果如下所示:

QE可以看出0.56?m间距像素的QE和串扰比0.61μm间距的参考像素有所改善,同时图像质量保持一致。最后文末给出了在4单元模式下使用0.56um像素拍摄的彩色图像示例,如下所示:

Demo图像

4. 结束语

在这项工作中,我们开发了一种新的28/40nm 2亿像素堆叠图像传感器,像素间距为0.56?m。该器件实现了5.5ke的FWC,没有图像滞后或光晕,暗性能与上一代0.61?m间距的器件相当。在可见光范围内,我们展示了比0.61?m更好的QPD QE性能。采用双列选择布局来提高读出速度,而不添加电路(位线),从而与上一代设备相比,帧速率有所提高。启用了可切换转换增益,使0.56?m器件的16C的FWC比之前的0.61?m器件高出2倍。好了今天就到这里,希望今天可以给您带来对于传感器的更深的认知,喜欢的同学可以进行朋友圈分享以及点击文章在看。另外,对论文感兴趣的同学可以follow我的Github论文仓库,也可以加入知识星球以及交流群,获取一手行业资料~加入星球:

|手机版|小黑屋|Archiver|汽车工程师之家

( 渝ICP备18012993号-1 )

|手机版|小黑屋|Archiver|汽车工程师之家

( 渝ICP备18012993号-1 )