基于FPGA的计算机防视频信息泄漏系统设计

以下为文章全文:(本站微信公共账号:cartech8)

汽车零部件采购、销售通信录 填写你的培训需求,我们帮你找 招募汽车专业培训老师

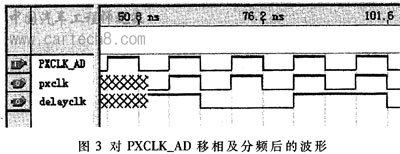

2.2 电磁兼容设计 2.2.1 信号完整性设计 系统中数字视频信号对传输时延要求较高,在布线时,其走线的路径要大体一致并且尽量短,以实现对传输时延的要求;合理安排去耦电容的摆放位置,尽可能接近所要进行去耦的电源;AD9883A芯片和ADV7125芯片周围电路的布线要尽可能短,周围的元器件要尽可能安排紧凑,以减小电流环路面积,从而减小静电干扰;放置过孔时,注意不要过密,以免损坏镜像层;适配卡所用的电阻、电容、电感和IC芯片均为表面帖装元件,有利于抑制电磁干扰。 2.2.2 电源完整性设计 系统所用的A/D转换器芯片、D/A转换器芯片对电源有严格的要求,除了要有模拟电源和数字电源之分外,AD9883A还要有PLL电路的专门电源,而FPGA电源要有内核电源和数字输出引脚的电源。因此,整个系统的电源设计是一个很大问题。这里用两片LT1 764作为FPGA的两种电源,用两片TPS76333作为AD9883A的两种电源,一片TPS76333作为ADV7125的电源。两块适配卡均 采用四层板结构,顶层和底层作为信号的走线层,中间层分别是地层和电源层,以确保系统在高速运行时有良好的电源环境。 3系统逻辑实现及仿真 FPGA芯片采用Altera公司Cyclone系列芯片EP1C6Q240C8。Cyclone系列芯片是基于1.5V,0.13μm工艺,具有时钟锁相环(PLL)和专用DDR接口,支持多种I/O标准的芯片。其内部嵌入了许多专用硬核模块,被广泛地用于可编程片上系统(SOPC)中。 本系统对高速图像信号进行处理,工作时钟近100MHz。为了获得更好的布线效果和系统性能,时钟信号必须经过锁相环到达全局时钟布线网络。本设计利用Altera公司的Maga Wizard设置Cyc lone PLL参数生成IPcore,解决了信号时延的问题,同时也满足了读取视频信号时所需的建立、保持时间要求。图3为使用FPGA内部PLL对输入的点频时钟PXCLK_AD进行相移后的波形,图中,pxclk与点频同频,经相位修复及幅度补偿后用作系统基准时钟,delayclk为点频三分频,用作延时时钟。

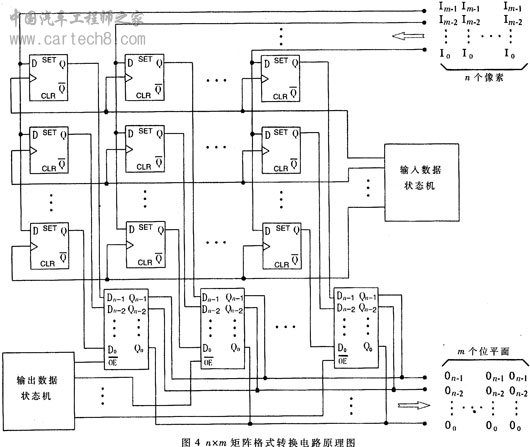

3.1 视频信息格式转换模块 在采集端适配卡中,视频信息由“像素包”格式转换为“位平面”格式,可由一个n×m矩阵转换电路完成,其输入数据总线宽度为m位,输出数据总线宽度为n位。系统工作时,每次要连续进行n次输入,即读入n个像素的数据,再连续进行m次输出,即把这些数据写到m个位平面所对应的各自的存储位置。格式转换电路原理如图4所示,采用一个n×m的D触发器阵列,再加上相应的输入和输出锁存电路及状态机控制电路,即可实现nxm数据格式转换。

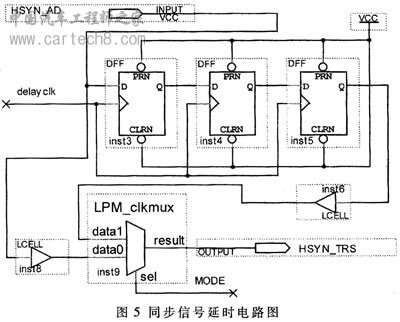

当第i个像素输入时,输入数据状态机触发第i行D触发器,第i个像素的第j位灰度信息就被存储在第i行的第m-1-j个D触发器中(i=1,2,…,n,j=0,1,…,m-1),n个像素全部输入完毕后,n×m位二进制信息就全部存储在n×m个D触发器中。此时,第i行D触发器中存储的是第i个像素的m位灰度信息,即“像素包”格式信息,第j列D触发器中存储的是n个像素的第m-1-j位灰度信息,即“位平面”格式信息。输出数据状态机按一定顺序输出某一列D触发器中数据,即可实现“位平面”数据的输出。视频信息由“位平面”格式转换为“像素包”格式原理与上述矩阵电路相似,限于篇幅在此不再介绍。 3.2 同步信号延时模块 同步信号是一定频率的脉冲串,与视频信号存在严格的同步关系,其频率与显卡设定的显示分辨率和屏幕刷新率有关。在进行视频信息格式转换过程中,视频信息共延时了约九个点频周期。为了使视频信息进入显示设备时与行、场同步信号间的相互时序关系仍能够保持完好,行、场同步信号均需通过延时模块进行处理。图5为采集端适配卡中行同步信号延时电路图。本系统由两块适配卡组成,两块适配卡中行、场信号延时电路相似。

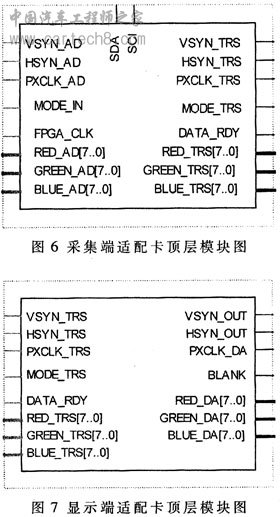

3.3 系统顶层模块 整个防视频信息泄漏系统设计完成后,其顶层模块如图6和图7所示。图中,SCI、SDA用来初始化AD9883A芯片,DATA_RDY为自定义的视频信息转换完毕信号。

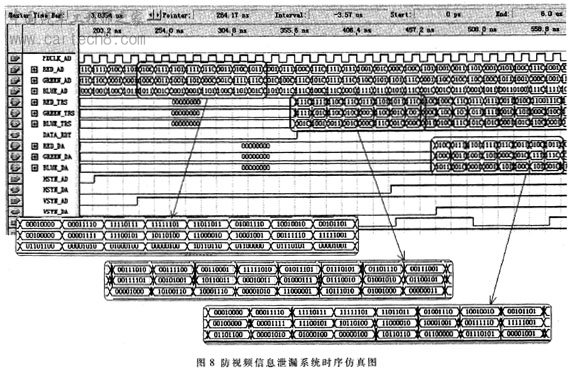

两块适配卡中都有格式转换电路,视频信息经过了两次格式转换后,最终还原为初始的“像素包”格式数据。取输入点频PXCLK_AD为78.75MHz,运用Quartus II进行综合及时序仿真后,两个顶层模块综合仿真的结果如图8所示,图中,三组数据依次为“像素包”格式、“位平面”格式、“像素包”格式。

|

文章网友提供,仅供学习参考,版权为原作者所有,如侵犯到

你的权益请联系542334618@126.com,我们会及时处理。

会员评价:

共0条 发表评论